全面解析FPGA基础知识

- 时间:2020-04-15作者:深圳市科电电子有限公司浏览:384

1)、 FPGA简介

FPGA普遍用于实现数字电路模块,用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的需求。它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。可以毫不夸张的讲,FPGA能完成任何数字器件的功能,下至简单的74电路,上**性能CPU,都可以用FPGA来实现。FPGA如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。

2)、FPGA整体结构

FPGA架构主要包括可配置逻辑块CLB(Configurable Logic Block)、输入输出块IOB(Input Output Block)、内部连线(Interconnect)和其它内嵌单元四个部分。

CLB是FPGA的基本逻辑单元。实际数量和特性会依器件的不同而改变,但是每个CLB都包含一个由4或6个输入、若干选择电路(多路复用器等)和触发器组成的可配置开关矩阵。开关矩阵具有高度的灵活性,经配置可以处理组合型逻辑、移位寄存器或 RAM。

FPGA可支持许多种I/O标准,因而可以为系统设计提供理想的接口桥接。FPGA 内的I/O按bank分组,每个bank能独立支持不同的I/O标准。目前较先进的FPGA提供了十多个I/O bank,能够提供灵活的I/O支持。

CLB 提供了逻辑性能,灵活的互连布线则负责在CLB和I/O之间传递信号。布线有几种类型,从设计用于专门实现 CLB 互连(短线资源)、到器件内的高速水平和垂直长线(长线资源)、再到时钟与其它全局信号的全局低skew布线(全局性**布线资源)。一般,各厂家设计软件会将互连布线任务隐藏起来,用户根本看不到,从而大幅降低了设计复杂性。

一般来说,器件型号数字越大,表示器件能提供的逻辑资源规模越大。在FPGA器件选型时,用户需要对照此表格,根据业务对逻辑资源(CLB)、内部BlockRAM、接口(高速Serdes对数)、数字信号处理(DSP硬核数)以及今后扩展等多方面的需求,综合考虑项目较合适的逻辑器件。

3)、FPGA开发流程

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。

1、功能定义/器件选型:在FPGA设计项目开始之前,必须有系统功能的定义和模块的划分,另外就是要根据任务要求,如系统的功能和复杂度,对工作速度和器件本身的资源、成本、以及连线的可布性等方面进行权衡,选择合适的设计方案和合适的器件类型。

2、 设计输入:设计输入指使用硬件描述语言将所设计的系统或电路用代码表述出来。较常用的硬件描述语言是Verilog HDL。

3、 功能仿真:功能仿真指在逻辑综合之前对用户所设计的电路进行逻辑功能验证。仿真前,需要搭建好测试平台并准备好测试激励,仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化。如果发现错误,则返回设计修改逻辑设计。常用仿真工具有Model Tech公司的ModelSim、Sysnopsys公司的VCS等软件。

4、 逻辑综合:所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。

5、布局布线与实现:布局布线可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的较佳布局,选择逻辑与输入输出功能链接的布线通道进行连线,并产生相应文件(如配置文件与相关报告);实现是将综合生成的逻辑网表配置到具体的FPGA芯片上。由于只有FPGA芯片生产商对芯片结构较为了解,所以布局布线必须选择芯片开发商提供的工具。

6、编程调试:设计的最后一步就是编程调试。芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generaon),将编程数据加载到FPGA芯片中;之后便可进行上板测试。最后将FPGA文件(如.bit文件)从电脑下载到单板上的FPGA芯片中。

4)、如何使用FPGA

FPGA开发完毕,较终得到验证好的加载文件。输出加载文件后,即可开始正常业务处理和验证(以软件加载方式为例,描述整个过程)

1、逻辑加载;

2、单板软件加载逻辑后,需要复位逻辑;

3、复位完成后,软件需等待等待一段时间至逻辑锁相环工作稳定;

4、软件启动对逻辑的外部RAM、内部Block RAM、DDRC等的自检操作;

5、软件完成自检以后,对逻辑所有可写RAM空间及寄存器进行初始化操作;

6、初始化完毕,软件参考逻辑芯片手册配置表项及寄存器;

7、逻辑准备好,可以开始处理业务。

5)、FPGA适用场景

FPGA适合非规则性多并发、密集计算及协议解析处理场景,例如人工智能、基因测序、视频编码、数据压缩、图片处理、网络处理等各领域的加速。

深圳市科电电子有限公司专注于FPGA厂家,sensor厂家,LDO厂家,UVC,储存快充芯片,环境光距离传感器等

词条

词条说明

取样电压加在放大器A的反相输入端,与加在同相输入端的基准电压Uref相比较,两者的差值经放大器A放大后,控制串联调整管的压降,从而稳定输出电压。当输出电压Uout降低时,基准电压与取样电压的差值增加,比较放大器输出的驱动电流增加,串联调整管压降减小,从而使输出电压升高。相反,若输出电压Uout**过所需要的设定值,比较放大器输出的前驱动电流减小,从而使输出电压降低。供电过程中,输出电压校正连续进行,

LDO即low dropout regulator,是一种低压差线性稳压器。这是相对于传统的线性稳压器来说的。传统的线性稳压器,如78XX系列的芯片都要求输入电压要比输出电压至少高出2V~3V,否则就不能正常工作。但是在一些情况下,这样的条件显然是太苛刻了,如5V转3.3V,输入与输出之间的压差只有1.7v,显然这是不满足传统线性稳压器的工作条件的。针对这种情况,芯片制造商们才研发出了LDO类的电

1. 导言现阶段市面上无论哪些电子设备,只需牵涉到电就务必使用开关电源,电源的归类有很多种多样,例如开关电源电路、变频电源、交流电这些。在手机端消费性电子设备中,常见的有DCDC电源和LDO开关电源二种,DCDC的特点是高效率,可是噪声大;LDO正相反,它是高效率低,噪声小。这二种开关电源实际在什么情景下应用不可以一概而论,通常来讲,针对噪声不特别敏感的数字电路设计多可以首先考虑到DCDC,而针对

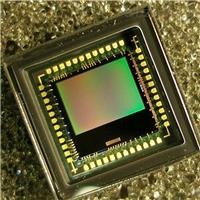

这些设备(如IDS生产的USB UVC相机)的优点是它们在运行时不需要安装特殊的驱动程序,因为标准的UVC驱动程序能让不同制造商生产的产品之间可相互兼容。因此,用户只需将相机连接到电脑上,便可直接进行图像传输。支持 USB Video Class (UVC) standard 1.1可以让相机在所有的作业系统以及平台中使用(Windows, Linux, Mac etc.)。用户只需连接相机便可进

联系方式 联系我时,请告知来自八方资源网!

公司名: 深圳市科电电子有限公司

联系人: 聂绍明

电 话: 13243662666

手 机: 13823729687

微 信: 13823729687

地 址: 广东深圳宝安区31区水口花园6片37号205

邮 编:

相关推荐

相关阅读

1、本信息由八方资源网用户发布,八方资源网不介入任何交易过程,请自行甄别其真实性及合法性;

2、跟进信息之前,请仔细核验对方资质,所有预付定金或付款至个人账户的行为,均存在诈骗风险,请提高警惕!

- 联系方式

- 相关企业

- 深圳市宇正芯科技有限公司

- 深圳市恒辰微电子有限公司

- 深圳市光达电子有限公司

- 四川芯毅光通信科技有限公司

- 深圳市岳邦电子科技有限公司

- 深圳市沃德一佳科技有限公司

- 深圳市悦为光电科技有限公司

- 深圳市鑫永诚光电科技有限公司

- 泉州市速冠电子科技有限公司

- 宁波市浩天电子有限公司

- 商家产品系列

- 产品推荐

- 资讯推荐