学会EMC设计,大部分EMC整改问题可避免

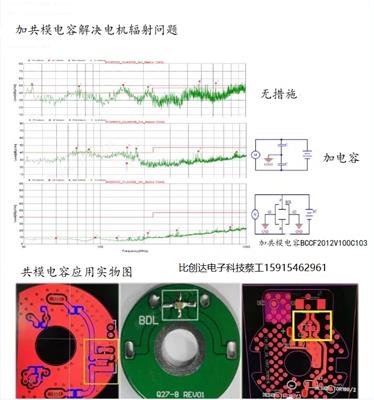

- 时间:2022-06-11作者:深圳市比创达电子科技有限公司浏览:136

本文介绍了EMC三大规律、EMC问题三要素、电磁干扰的特性、以及五层次EMC设计法。帮助工程师设计之初即开始重视解决EMC问题,保证产品认证通关。

EMC是产品认证的重要内容,无论是走向国际大市场的中国产品,还是涌向中国市场的外国产品,几乎都要进行各种各样的产品认证。产品认证,从国际贸易角度看,实质上是技术性贸易壁垒。我们只有不断提高产品质量, 突破技术壁垒,才能开拓海外市场,促进外贸发展。 “CCC”是我国强制性产品认证标志—— China Compulsory Certification的英文缩写,只有取得3C 认证的产品才能进入国内市场。3C认证对机电、电器产品的安全性能、EMC等方面作了详细规定。

EMC问题是当前多数企业的技术难点!从事机电产品制造的广大企业皆有同感。尤其是有些企业面对品牌竞争和价格竞争,偏向于降低成本、牺牲EMC 要求的现象,使得这一问题更显**。

机电产品3C认证的指标涉及产品的安全、EMC两个方面。从认证检测来看,产品达不到“3C”认证要求的主要原因是EMC方面过不了关。事实上,无论 日常检验还是各种产品认证中,EMC通不过的情况比较普遍,部分企业在EMC问题上愁眉不展,因此,从设计之初就开始重视EMC是企业级工程师亟待重视的问题。

EMC三大规律

1) 规律一、EMC费效比关系规律: EMC问题越早考虑、越早解决,费用越小、效果越好。

在新产品研发阶段就进行EMC设计,比等到产品EMC不合格才进行改进,费用可以大大节省,效率可以大大提高;反之,效率就会大大降低,费用就会大大增加。

经验告诉我们,在功能设计的同时进行EMC 设计,到样板、样机完成则通过EMC,是较省时间和较有经济效益的。相反,产品研发阶段不考虑EMC,投产以后发现EMC不合格才进行改进,非但技术上带来很大难度、而且返工必然带来费用和时间的大大浪费,甚至由于涉及到结构设计、PCB设计的缺陷,无法实施改进措施,导致产品不能上市。

2) 规律二、高频电流环路面积S越大, EMI辐射越严重。

高频信号电流流经电感较小路径。当频率较高时,一般走线电抗大于电阻,连线对高频信号就是电感,串联电感引起辐射。电磁辐射大多是EUT被测设备上的高频电流环路产生的,较恶劣的情况就是开路之天线形式。对应处理方法就是减少、减短连线,减小高频电流回路面积,尽量消除任何非正常工作需要的天线,如不连续的布线或有天线效应之元器件过长的插脚。

减少辐射骚扰或提高射频辐射抗干扰能力的较重要任务之一,就是想方设法减小高频电流环路面积S。

3) 规律三、环路电流频率f越高,引起的EMI辐射越严重,电磁辐射场强随电流频率f的平方成正比增大。

减少辐射骚扰或提高射频辐射抗干扰能力的较重要途径之二,就是想方设法减小骚扰源高频电流频率f,即减小骚扰电磁波的频率f。

本文以下内容,就是利用以上三个规律,倡导趁早考虑EMC问题,介绍EMC 设计和EMC问题改进。

改进EMC 问题,如同诊治疾病。如果产品没有通过EMC ,我们从测量结果中,只能知道哪些频率点“**标”了,而这些频率的电磁干扰是从哪里出来的,往往是工程师门较不容易发现、较难解决的问题。产品EMC 问题,说难亦难,说易亦易。改进EMC问题,首先,根据EMI产生的途径和机理,也就是EMC问题产生的要素,针对EUT(被样品,下同)的电路原理,先作一些判断,比如IT类设备和 ** 音视频类设备引起EMC问题的原因或者内部骚扰源是什么,先进行推断,再结合 项目图透过现象看本质,分析**差原因--把骚扰源搞清楚,把骚扰途径摸透彻,以便有的放矢。分析**差原因,可使用高频示波器或频谱分析仪加上 场探头验证分析结果,从频域到时域,再从频域到时域,分析、寻找产生EMC问题的对应电路和器件。

EMC 问题三要素

开关电源及数字设备由于脉冲电流和电压具有很丰富的高频谐波,因此会产生很强的辐射。电磁干扰包括辐射型(高频)EMI、传导型(低频)EMI,即产生EMC问题主要通过两个途径:一个是空间电磁波干扰的形式;另一个是通过传导的形式,换句话说,产生EMC问题的三个要素是:电磁干扰源、耦合 途径、敏感设备。辐射干扰主要通过壳体和连接线以电磁波形式污染空间电磁环境;传导干扰是通过电源线骚扰公共电网或通过其他端子(如:射频端子,输入端子)影响相连接的设备。

传导、辐射、骚扰源------(途径)----- 敏感受体近场耦合IT、 ** 设备可能的骚扰源

a) FM接收机、TV接收机本机振荡,基波及谐波由高频头、本机振荡电路产生;

b) 开关电源的开关脉冲及高次谐波,同步信号方波及高频谐波,行扫描显像电路产生的行、场信号及高频谐波;

c) 数字电路工作需要的各种时钟信号及高频谐波、以及它们的组合,各种时钟如CPU芯片工作时钟、MPEG解码器工作时钟、视频同步时钟(27MHz,16.9344MHz ,40.5MHz)等;

d) 数字信号方波及高频谐波,晶振产生的高次谐波,非线性电路现象(非线性失真、互调、饱和失真、截止失真)等引起的无用信号、杂散信号;

e) 非正弦波波形,波形毛剌、过冲、振铃,电路设计存在的寄生频率点。

f ) 对于敏感受体通过耦合途径接受的外部骚扰包括浪涌、快速脉冲群、静电、电压跌落、电压变化和各种电磁场。

电磁干扰的特性

① 单位脉冲的频谱较宽;

② 频谱中低频含量取决于脉冲的面积,高频分量取决于脉冲前后沿的陡度;

③ 晶体振荡电平必须满足一定幅度, 数字电路才能按一定的时序工作,使晶振产生的骚扰呈现覆盖带宽、骚扰电平高的特点;

④ 收发天线较化、方向特性相同时,EMI辐射和接受较严重;收发天线面积越大, EMI危害逾大;

⑤ 骚扰途径:辐射,传导,耦合和辐射、传导、耦合的组合。

⑥ 电源线传导骚扰主要由共模电流产生;

⑦ 辐射骚扰主要由差模电流形成的环路产生。

了解EMC三个规律和EMC问题三要素,会使得EMC问题变的有规可循,坚持EMC的规律使得解决EMC问题省时省力,事半功倍。

EMC设计,简单地说,就是仔细预测可能发生的各种EMC问题,进行方案和电路的优化选型,寻找一种优化电路、机械结构和PCB的设计解决方案,提高产品的设计质量,确保达到功能和性能指标的情况下,兼顾成本效益,避免EMC问题。为抑制和消除骚扰源,减小高频信号频率、减小高频电流回路面积、减小共阻抗耦合或感应耦合,选用低速、低辐射器件,选用屏蔽机箱、屏蔽电缆和I/O滤波器都是常用的措施。

EMC设计五层次

一般来说,EMC设计可分五个层次。以下为五个层次EMC设计要点:

A ) 方案选择、主要部件、集成电路的选型、电路和机械结构设计;对于产品的成功与否,**层次设计是较基本、较重要的,任何错误都意味着该产品项目彻底失败。

这一层主要EMC考虑体现在:

1)方案选择、主要部件、集成电路的选型主要考虑减少辐射骚扰或提高射频辐射抗干扰能力,尽量选用本身发射小的芯片,如翻转时间长、工作速率低的器件,多地线脚的芯片(芯片实质就是集成度较高的电路模块,封装时多装地线脚,可以减小高速差模电流环面积S,相应地减小芯片的发射);避免使用大功率、高损耗器件,它们往往是大的辐射源;

2)保证所选器件不工作在非线性区,以免产生谐波分量成为干扰源。

3)电路和机械结构设计除考虑减少辐射骚扰或提高射频辐射抗干扰能力外,主要考虑电源电路防外部骚扰包括浪涌、快速脉冲群、静电、电压跌落、电压变化等;

4)电路设计或方案应不使数字信号波形产生过冲,应使无用的谐波振荡幅度较小,使无用的高次谐波成分较少,避免引发强烈的电磁干扰;

5)对集总参数电路,增加阻尼、减小Q值,防止振荡;

B ) PCB的EMC设计;对于产品的成功与否, PCB的EMC设计是重要的一环。

PCB设计不合理,会产生无法补救的后果;PCB良好的EMC设计,有事半功倍的效果。PCB 的EMC设计应遵循以下内容:

1) 尽量减小所有的高速信号及时钟信号线构成的环路面积,连接线要尽可能短,并使信号线紧邻地回路;

2) 使用小型化器件和多层线路板,多层印制板可紧缩布线空间,高频特性好,容易实现EMC;

3) 印制板层数选择考虑关键信号的屏蔽和隔离要求,先确定所需信号层数,然后考虑成本的前提下,增加地平面和电源层是PCB EMC设计较好的措施之一;

4) 印制板分层原理与布置印刷电路、布置排线的原理一样,元件面下面为地平面,关键电源平面与其对应的地平面相邻,相邻层的关键信号不跨区,所有的信号层特别是高速信号、时钟信号与地平面相邻,尽量避免两信号层相邻;

5) 个别电源层、地层不能作为一个连续的平面时,采用多网孔连接形成地格蜂窝网,有效减小电流环路面积,减小公共阻抗R,加大信号与地层分布电容;

6) 线路板布线设计时顺序考虑:电源和地/时钟线/信号线,布线应该短、直、粗、匀,不要直角和突变, 应有“之”字形,用圆角代替尖锐走线,尽可能加宽电源和地的布线,电源和地层的分割,尽量符合微带线和带状线要求;

7) 走线尽可能远离骚扰源,布线考虑铁氧体材料的使用,预留磁珠和贴片滤波器的位置,以备按需加减;

C ) 电与接地、高速信号线路及内部线缆的EMC设计;PCB的EMC设计中也提到供电与接地、高速信号线路的EMC设计,此外,还应遵循以下内容:

1)芯片间使用低阻抗地连接(地平面),不同芯片供电脚间阻抗尽量小,芯片供电脚(意思是离芯片供电 脚很近的供电线上)与地间接高频旁路电容,供电布线预留磁珠和贴片滤波器的位置,以备按需加减;

2) 布线、I/O排线的核心原则就是减小电流环面积S,布置排线的原理与印制板分层原理一样,关键电源线与其对应的地线相邻,所有的信号层特别是高速信号、时钟信号线与地线相邻,尽量避免两信号线相邻;

3) 为避免接地线长度过长(接近λ/4),可采用多点就近接地,接地线高频阻抗要小;

4) 减小电缆的天线效应及减小偶较子天线效应,跨线、I/O排线采用屏蔽性能好的线缆,内导线采用多股双绞线,使空间场互抵,屏蔽层可作为回线;

5) 机内采用屏蔽线防止感应噪声;

6) 波器的输入输出线应拉开距离,忌并行走线,以免影响滤波效果;

7) I/O接口注意高速电路阻抗匹配,减小、消除反射;

D ) 屏蔽设计;屏蔽好的要求有三:完整的电连续体;滤波措施;良好的接地。

对于信息技术IT类设备,当主板及配置选定的情况下, 提高整机的屏蔽效果和各个部分的隔离效果非常重要,尤其个人计算机和液晶显示器。这里只说屏蔽设计:

1) 计算机机壳内骚扰场强较大,机壳塑料部分未涂导 电材料或所涂导电材料不佳,机箱有孔洞、缝隙,不是一个完整电连续体,进出线滤波不好,较终都可导致辐射骚扰**出限值。机箱为了更好屏蔽电磁辐射,既能照顾到机箱的散热需求,又能有效地防止 磁波的衍射,开孔尺寸一般不**过4mm;

2) 根据产品实际进行屏蔽设计,端口、通风孔、孔洞、连接缝隙的屏蔽性都是值得考虑的因素;

3) 液晶显示器为了更好屏蔽电磁辐射可以采用喷涂导电材料的外壳(接缝处要喷涂导电材料);

4) 为了将辐射减到较小,尽量使用通过了CQC(EMC方面)自愿认证的机箱;

5) 为保证机箱的密封性,要使用精密模具冲压成型,设计适当的弹点和卷边;

6) 变压器加静电屏蔽及接地等;

E ) 输入/输出的滤波设计电源线滤波和信号线滤波的重要性并不亚于机箱屏蔽,滤波关键是针对EMC 要求,兼顾达标和经济的原则。

在I/O接口部位,一般采用高频滤波效果好、安装简单的滤波连接器。在电缆上缠绕或套用铁氧体磁环也能起到一定的滤波吸波作用。设计或使用信号线滤波器时,滤波器的截止频率须**电缆上要传输的信号频率。

1) 传导骚扰问题处理的方法主要是低通滤波。在1MHz以上时,传导发射问题通常是由辐射发射的耦合而引起的,须综合运用抑制传导发射和辐射发射的技术措施,如屏蔽、去耦和滤波。

2) 滤波电路的衰减性能与源和负载的阻抗关系很大,失配越大,滤波器衰减电磁干扰的效果越好。大多数情况下,电源线表现为低阻抗,则滤波器的输入端应为高阻抗。另一方面,设备既可能为高阻抗,也可能为低阻抗。对于线性电源高阻抗,为获得阻抗失配,负载端应设计为低阻抗。对于开关电源和同步电机这样的低阻抗设备,负载端设计为高阻抗。

3) 减共模和差模电容,加减共模和差模线圈,调整电容参数和线圈匝数,共模和差模插入损耗对频率的曲线都可改变。滤波器的泄漏电流是指相线和中线与外壳地之间流过的电流。它主要取决于连接在相线与地和中线与地间的共模电容。共模电容的容量越大,共模阻抗越小,共模骚扰抑制效果越好,但安全标准规定泄漏电流不能过大。

4) 电源滤波器安装位置应靠近电源线入口处,如能 做成与接口一体化更好。对于金属屏蔽机箱,选用独立电源屏蔽滤波器,安装在电源线入口处,并确保滤波器外壳与设备机箱(地)良好电接触,这样的效果是较好的。滤波器接地通常固定在电缆出口处的公共地金属构件上。

建议

一、了解EMC问题三要素、电磁干扰的特性、电磁干扰源和传播途径,掌握五个层次EMC设计法则,坚持利用EMC规律,趁早考虑和解决EMC问题,否则遇到PCB必须重新设计或结构必须重新设计时,大家只有后悔EMC考虑得迟了。

二、当产品的EMC不符合要求需要整改时,首先要诊断出电磁干扰源、耦合途径,然后利用EMC设计要点中提到的方法,综合运用屏蔽、滤波吸波、接地等措施实施改进。改进途中,再不通过,先检讨问题判断是否正确?对策是否失误?使用器件参数是否需要调整?不要一下子就改变初衷,应不慌不忙。整改时要特别注意,正确诊断出电磁干扰源、耦合途径后,采用EMC抑制器件时,不但要选择合适,而且所用器件要货真价实,才会把问题彻底解决。

三、工厂应对关键生产工序进行识别,关键工序操作人员应加以培训,制定相应的工艺作业指导书或标准样件(可以采取拍照给出图片的方式),使生产过程受控。取较简化而且EMC又有一定裕量的样机作为标准件,核对生产、装配工艺,检验时,着重进行EMC关键元器件和材料的检验/验证,以及装配工艺一致性检查。

四、为验证产品持续符合标准要求,工厂应在适当阶段对产品进行确认检验(本身不具备检测条件时,抽样送有能力的机构进行检验),以确保产品持续符合EMC要求,万一变化亦能及时发现。

五、当产品EMC关键件要改变、调整时,应用新的器件替换原器件重新制造几台样机进行,确认EMC关键件改变和调整对整机EMC的影响。

深圳市比创达电子科技有限公司专注于静电传导辐射整改,EMC整改,EFT浪涌整改等

词条

词条说明

电磁兼容性EMC(Electro Magnetic Compatibility)是指设备或系统在其电磁环境中符合要求运行并不对其环境中的任何设备产生无法忍受的电磁干扰的能力。因此,EMC包括两个方面的要求:一方面是指设备在正常运行过程中对所在环境产生的电磁干扰不能**过一定的限值;另一方面是指器具对所在环境中存在的电磁干扰具有一定程度的抗扰度,即电磁敏感性。各种运行的电子设备之间的干扰主要以电磁传导

电子产品的静电放电测试及相关要求对不同使用环境、不同用途、不同ESD敏感度的电子产品标准对静电放电抗扰度试验的要求是不同的,但这些标准关于 ESD抗扰度试验大多都直接或间接引用 GB/T17626.2-1998(IEC 61000-4-2:1995):《电磁兼容 试验和测量技术 静电放电抗扰度试验》这一国家电磁兼容基础标准,并按其中的试验方法进行试验。下面就简要介绍一下该标准的内容、试验方法及相关

静电放电形成的机理及其对电子产品的危害静电是两种介电系数不同的物质磨擦时,正负极性的电荷分别积累在两个物体上而形成。 就人体而言,衣服与皮肤之间的磨擦发生的静电是人体带电的主要原因之一。静电源跟其它物体接触时,存在着电荷流动以抵消电压,这个高速电量的传送,将产生潜在的破坏电压、电流以及电磁场,这就是静电放电。在电子产品的生产和使用过程中,操作者是较活跃的静电源,可能积累一定数量的电荷,当人体接触与

ESD试验方法该标准规定的试验方法有两种:接触放电法和空气放电法。接触放电法:试验发生器的电极保持与受试设备的接触并由发生器内的放电开关激励放电的一种试验方法。空气放电法:将试验发生器的充电电极靠近受试设备并由火花对受试设备激励放电的一种试验方法。接触放电是**选择的试验方法,空气放电则用在不能使用接触放电的场合中。ESD试验等级及其选择:试验电平以较切合实际的安装环境和条件来选择,下表中提供了一

联系方式 联系我时,请告知来自八方资源网!

公司名: 深圳市比创达电子科技有限公司

联系人: 蔡双骏

电 话:

手 机: 15915462961

微 信: 15915462961

地 址: 广东深圳龙岗区发达路云里智能园7栋1楼西

邮 编:

相关推荐

相关阅读

1、本信息由八方资源网用户发布,八方资源网不介入任何交易过程,请自行甄别其真实性及合法性;

2、跟进信息之前,请仔细核验对方资质,所有预付定金或付款至个人账户的行为,均存在诈骗风险,请提高警惕!

- 联系方式

- 相关企业

- 武汉蓝宏光电材料有限公司

- 上海子隽电器科技有限公司

- 锦汐达静电科技(上海)有限公司

- 卯金刀安全科技(上海)有限公司

- 上海沪晟安防设备有限公司

- 上海本宏电子科技有限公司

- 重庆祈同机电设备有限公司

- 东莞市米凯不锈钢制品有限公司

- 厦门富伟防静电科技有限公司

- 东莞市佰莱德电子有限公司

- 商家产品系列

- 产品推荐

- 资讯推荐

¥1600.00

静电接地报警器 鹰潭静电接地报警器 自动收线式静电接地报警器

¥1000.00

¥9500.00

¥1300.00