CMOS微缩结束了吗?

- 时间:2022-12-07作者:深圳海木芯科技有限公司浏览:122

不可否认的是,CMOS的微缩已经成为推动过去几十年的巨大进步的“燃料”,以提高性能、效率和降低集成电路和系统的成本,从而实现新的应用。摩尔定律的终结已经被预言了很多次,而材料、设备概念和图案的创新已经为当前的10nm以下技术扫清了道路。然而,该行业已经到了这样一个阶段:

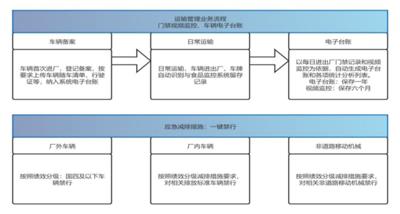

过去50年的规模化所带来的功耗、性能、面积和成本(PPAC)方面的典型收益已经变得越来越难以实现,尤其是在展望未来3nm技术的时候。随着22nm FinFET的引入,我们已经清楚地认识到,单纯的尺寸缩放不足以满足半导体经济的需求。设计-技术协同优化(DTCO)的概念(如图1),其中可扩展到功能块的级别,已经获得了很大的吸引力,目前越来越多地成为工业中用于评估技术权衡和挑战下一代精细设计规则的标准方法。

例如,在3nm处,通过缩放栅较间距和金属间距所减少的面积较多只有34%,而所需的比例为50%。因此,已经提出了有助于减少电池缩放的特殊构造,如埋入式电源轨道,通过将电力线嵌入隔离的线路(FEOL)或衬底,标准单元的轨道高度可以从6轨道(6T)缩放到5轨道(5T)。

图1:从传统的维度标度到设计技术协同优化(DTCO)导向标度到系统技术协同优化(STCO)。

从器件架构的角度来看,FinFET(图2a)仍然是人们感兴趣的主要器件概念,但单元高度缩放正在迫使FIFIN减少。将每个器件的FIFIN数从两个FIFIN减少到一个FIFIN,从而显著地削弱了器件强度并增加了可变性。通常可以通过增加FIFIN高度来恢复器件强度。然而,这通常会增加工艺和集成的复杂性,从而使这些高纵横比薄膜的机械稳定性开始下降。

图2:3nm器件结构的优化 (a)高纵横比FinFET的TEM图像,(b)堆叠纳米片器件的TEM图,(c)分叉片(Forksheet)的示意图,(d)互补场效应晶体管(CFET)的原理图。

类似纳米片 (图2b)这样的衍生结构(硅通道的薄板相互堆叠)引起了人们的较大兴趣,因为这些设备不仅提供了更好的静电学,而且还提高了相对于finfet的性能效率,从而实现更短的栅较长度、更高的每个足迹的驱动电流,以及对特定的接触电阻率等元素的更轻松的要求。但是,n- p分离的挑战仍然存在,这限制了cell footprint的进一步减少。在FinFETs中,栅较过度活跃的扩展基本上限制了SRAM单元高度的降低,因为栅较需要完全覆盖垂直的侧壁。因此,提出了一种新的设备架构:Forksheet(图2c)。在栅较图案形成之前,叉形栅较结构依赖于在NMOS和PMOS之间形成一层介电墙,从而形成自然屏障,使栅较和触点同时自对准。它消除了器件一侧的门较过扩展边缘,允许它将门较边缘与通道自对准,从而比标准的纳米片布局减少了20%的位单元。

纳米片的一个更具性的进展是互补的FET或CFET(图1.3.2d),其中NMOS堆叠在PMOS之上。该装置的概念特别针对单元的互补性质,从而完全消除了n- p分离的瓶颈。该结构允许面积增益高达50%的标准电池以及SRAM,使它成为一个可能的总CMOS微缩解决方案。集成方案可以嫁接在一个典型的门式全流程flflow,也可以使用顺序3D处理,这是一种薄片级3D处理的薄片,它允许不同层之间以同样的分辨率和密度进行连接,而高级光刻技术可以为标准的后端金属化(BEOL)提供同样的分辨率和密度。

CFET基本上是开发*三维度的第一步。单个CMOS技术通常实现系统(SoC)中的所有功能。如今,更多的趋势是定制化设计,为所需的功能挑选较好的技术,并将其与系统的其他部分很好地结合在一起,这些部分通常非常不同,而不是采用一种通用的技术。这种异构集成需要设置与DTCO类似的方法,但是要将抽象级别提升到(子)系统:STCO,在STCO中跨许多不同级别进行优化,从流程单元步骤和集成一直到应用程序级别(图1.3.1)。下面将列举几个例子。

异构集成与3D技术ML、5G、AR/VR等新兴应用将需要启用多种功能(内存计算、**低功耗、高速等)。对将这些不同技术融合在一起的混合微缩的需求越来越大。以前作为缩放路线图的一部分而考虑的器件概念,由于不是完整的CMOS解决方案而被放弃,现在在其他应用的背景下和异构集成的背景下被再次考虑。

一个例子是用于机器学习的电阻式RAM(RRAM)。*二个例子与化合物半导体的使用有关,如GaN和III-V族化合物。在寻求能够在降低电源电压的情况下提供更高速度的逻辑晶体管的过程中,这些材料由于具有更高的迁移率和饱和速率,被认为是MOSFET中Si沟道的替代材料。在过去的十年中,他们在CMOS兼容的Si基板上的co集成、与栅较堆栈相关的可靠性和可扩展性方面的挑战一直是一般研发工作的重点。

虽然越来越明显,这些设备的性能在ultra-scaled维度将无法与成熟的Si FinFET技术的进展已经协整的这些不同的材料如果平台带头再考虑他们作为其他应用程序的可行的选项(高压和射频应用程序),但这一次添加的优势能够制造CMOS-compatible生产线。

在高压应用方面,与GaN-on-SiC相比,GaN-on-Si在过去几年中获得了大量的发展,它是一种成本效益更佳的选择,可以升级到比6英寸更大的基片,同时在比LDMOS更高的频率上提供更高的输出功率。GaN高压领域的发展趋势与热膨胀(CTE)匹配基板的系数有关,这些基板追赶了Si,但仍然与CMOS工艺兼容。

新的设备概念,如允许高击穿电压和高单位面积电流的半垂直设备,改进的可靠性和更容易的热管理,以及从独立组件转移到GaN- ic选项,在GaN层启用更多的功能(图3)。

图3:采用深沟槽隔离的GaN-on- soi工艺的原理图,使不同的GaN集成在同一衬底上。

除此之外,GaN或III-V器件具有高片状电荷、高电子迁移率和宽带隙等*特的特性,因此通常也非常适合于高频应用。5 g部署和已经下一代无线通信更高数据速率在哪里设想(> 100 gb / s),有明显的担忧增加的复杂性相关射频Front-End-Module (RF-FEM),特别是在毫米波频率越高,波束形成无线电架构需要相控阵列天线的使用。

深圳海木芯科技有限公司专注于IMX385,IMX290,IMX990,IMX991,IMX335,IMX253,lMX183,lMX264,AABJ-C,AABA-C等

词条

词条说明

CMOS的制作需要经过一系列的复杂的化学和物理操作,而做为一名集成电路版图(ic layout)工程师,系统的了解这个在半导体制造技术中具有代表性的CMOS工艺流程是非常有必要的。只有熟悉了工艺流程才会了解各层次之间的关系,才会在IC Layout的绘制中考虑到版图中各层次对流片产生的影响。1初始清洗将晶圆放入清洗槽中,利用化学或物理方法将在晶圆表面的尘粒或杂质去除,防止这些杂质尘粒对后续制造工艺

对摄像机来说,3CMOS(3片 CMOS)重要吗,与单片 CMOS 画质上区别有多大?

理论区别的话,基本上三片式结构( 3CCD 或者 3 CMOS )因为一个像素可以同时感三种颜色的光,对于光线的利用更为完全,同时不会有混色效应,所以比起拜尔矩阵拥有更好的锐度。三片式结构较早可以追溯到彩色胶片录影。通过分光把入射光线打到三个感不同颜色的胶片上。而到了数码时代只需要把胶片换成光电转换器件(如 CCD、CMOS 等)就行了,实际上**台数字电影摄影机就是 3CCD (蓝鲱鱼,阿莱和美

中国摄像头CMOS需求潜力旺盛CCD和CMOS在制造上的主要区别是CCD是集bai成在半导体单晶材料上du,而CMOS是集成zhi在被称做金属氧化物的半导体材料dao上,工作原理没有本质的区别。CCD只有少数几个厂商例如索尼、松下等掌握这种技术。而且CCD制造工艺较复杂,采用CCD的摄像头价格都会相对比较贵。事实上经过技术改造,目前CCD和CMOS的实际效果的差距已经减小了不少。而且CMOS的制造

1 MEMS 比 CMOS 的复杂之处MEMS 与 CMOS的根本区别在于:MEMS 是带活动部件的三维器件,CMOS 是二维器件。因此,虽然许多刻蚀和沉积工艺相似,但某些工艺是 MEMS *有的,例如失效机理。举个例子,由于 CMOS 器件没有活动部件,因此不需要释放工艺。正因为如此,当活动部件“粘”在表面上,导致设备故障时,就会产生静摩擦,CMOS 没有这种问题。CMOS 器件是在硅材料上逐层

联系方式 联系我时,请告知来自八方资源网!

公司名: 深圳海木芯科技有限公司

联系人: 张小姐

电 话:

手 机: 13760268219

微 信: 13760268219

地 址: 广东深圳南山区大冲一路华润置地E座33楼B

邮 编: 0

相关推荐

相关阅读

1、本信息由八方资源网用户发布,八方资源网不介入任何交易过程,请自行甄别其真实性及合法性;

2、跟进信息之前,请仔细核验对方资质,所有预付定金或付款至个人账户的行为,均存在诈骗风险,请提高警惕!

- 联系方式

- 相关企业

- 普兰店区中科安防设备经营处

- 桂林宇顺通智能设备工程有限公司

- 东莞市雅奋电子有限公司

- 宜春市乐平科技有限公司

- 深圳市以亚电子科技有限公司

- 周口市和营影视文化有限公司

- 山西天泽林文化艺术传播中心

- 惠州市人峰科技有限公司

- 西宁市照相有限公司

- 阳泉市添瑞信息技术有限公司

- 商家产品系列

- 产品推荐

- 资讯推荐