半导体材料SiC和GaN

- 时间:2020-04-10作者:仪准科技(北京)有限公司浏览:144

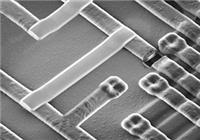

宽禁带半导体材料SiC和GaN 的研究现状 **代半导体材料一般是指硅(Si)元素和锗(Ge)元素,其奠定了20 世纪电子工业的基础。*二代半导体材料主要指化合物半导体材料,如砷化镓(GaAs)、磷化铟(InP)、磷化镓(GaP)、砷化铟(InAs)、砷化铝(AlAs)及其合金化合物等,其奠定了20 世纪信息光电产业的基础。*三代宽禁带半导体材料一般是指氮化镓(GaN)、碳化硅(SiC)、氮化铝(AlN)、金刚石等材料,其具有禁带宽度大、抗辐射能力强、击穿电场强度好、耐高温等特点,可以克服传统半导体的劣势,能够使设备在较端恶劣的条件下正常工作。因此,宽禁带半导体的材料可以在微电子领域发挥重要的作用,具有广阔的应用市场。 禁带宽度是半导体的一个重要特性参数,根据半导体材料的能带结构不同,可将半导体材料分成两种类型:宽禁带和窄禁带。若半导体材料的带隙宽度小于2.3eV,则称为窄带隙半导体,代表性材料有GaAs、Si、Ge 和InP ;若半导体材料的带隙宽度大于或等于2.3eV,则称为宽带隙半导体,代表性材料有GaN、SiC、AlN 和氮化铝镓(AlGaN)等。半导体材料的禁带宽度越大,意味着其电子跃迁到导带所需的能量越大,从而材料能承受的温度和电压越高,即越不容易成为导体。 宽禁带半导体材料非常适合于制作抗辐射、高频、大功率和高密度集成的电子器件,其具有良好的抗辐射能力及化学稳定性、较高的饱和电子漂移速度及导热率、优异的电性能等特点。近年来,*发展起来的以GaN、SiC 为代表的宽禁带半导体材料是固态光源和电力电子、微波射频器件的“核芯”,在半导体照明、新一代移动通信、智能电网、高速轨道交通、新能源汽车、消费类电子等领域具有广阔的应用前景,可望成为支撑信息、能源、交通、*等产业发展的重点新材料,进行宽禁带半导体材料的相关技术研发正在成为**半导体产业新的战略高地。SiC 与GaN 是*三代宽禁带半导体材料中发展比较成熟的材料,本文主要研究这两类材料。 SiC材料及其制备工艺 SiC 具有*特的物理和电学特性,其可以通过热氧化工艺制备出SiO2,同时在氧化过程中使C 元素以气体的形式释放,制备出高质量的SiO2,进而可利用SiC 制作性能优良的金属– 氧化物– 半导体(Metal-Oxide-Semiconductor,MOS)晶体管。 (一)SiC 材料结构及特性 SiC 为Ⅳ主族中Si 元素和C 元素组成的化合物,C 原子和Si 原子以共价键的形式连接。SiC 的基本结构单元是硅碳四面体,其相互连接形成各种紧密堆积的结构。Si—C 双原子层的堆积顺序不同,导致SiC具有多种晶体结构。其中,SiC 的同态多晶型主要有闪锌矿(Zincblende)结构、纤锌矿(Wurtzite)结构和菱形(Diamond)结构。SiC 的纤锌矿结构为α-SiC,SiC 的立方闪锌矿结构为β-SiC,根据晶体堆叠的不同呈现出多型结构,其中β-SiC(3C-SiC)和α-SiC(2H-SiC、4H-SiC、6H-SiC、15R-SiC)比较具有代表性,对于不同的晶体结构,其禁带宽度也有所差异,如图1 所示。 图1 SiC材料的常见多型结构(a)SiC材料的晶体结构;(b)对应的禁带宽度 在SiC 的各种晶体类型中,3C-SiC 键能较低,晶格自由能较高且易成核,但其处于亚稳态,具有较低的稳定性及易发生固相转移的特点。在接**衡态的条件下,当退火温度分别为1200℃和2000℃时,3C-SiC 会发生相变,部分转变为6H-SiC 和4H-SiC,其中3 种晶型的键能大小顺序为3C-SiC<6H-SiC< 4H-SiC,键能越小越不稳定,在外界条件影响下越*发生相变。所以,通过改变外界条件,3C-SiC 可以发生相转变,变成其他晶型。目前,应用较多的是4H-SiC 材料,其禁带宽度为3.2eV,是Si 禁带宽度的3 倍左右,且热导率高,故多用于高温大功率的微电子器件领域。 (二)SiC 晶体的制备 图2(a)为SiC 相图,可以看出,在大气氛围中SiC 在2830℃下会分解为C 和含C 量为13% 的Si 熔液,因此无法从Si-C熔融体中进行晶体生长。在过去的30 年中,工业界已研发出采用升华的方式制备SiC 衬底的技术,使SiC 材料在低压惰性环境中升华,Si、SiC2、Si2C 等分子沿温度梯度迁移,并按照设计取向在单晶SiC 种子层上沉积而重新结晶成SiC 晶体,如图2(b)所示。采用新的物理气相传输(PVT)技术能够将晶体制备温度控制在1900~2400℃范围内。 图2 SiC的相图(a)和制备SiC的物理气相传输(PVT)技术(b) SiC 存在各种多型体(结晶多系),它们的物性值也各不相同。SiC 晶体中存在多种缺陷,这些缺陷会降低其自身的质量。常见的晶体缺陷类型有微管、位错、层错、夹杂、多型共生等,如图3 所示。晶体缺陷给SiC 器件的应用造成了很大的阻碍。在这些缺陷当中,微管缺陷带来的后果较严重,SiC 器件的工作区域中任一微管缺陷都可能会导致器件的失效。 图3 常见的SiC晶体缺陷类型 虽然一些电子元器件能够在不使用外延层的情况下直接在衬底材料上制备,但高品质的SiC 器件仍然需要利用高品质的外延材料制备有源区。因此,低缺陷的SiC 外延生长技术对SiC器件质量有着重要的影响。随着SiC 功率器件制造要求和耐压等级的不断提高,其外延材料不断向低缺陷、厚外延方向发展。目前,批量生产SiC 外延材料的产业化公司有美国的CREE、Dow Corning,日本昭和电工(Showa Denko)等。 GaN材料及其制备工艺 在理论上,GaN 材料的击穿电场强度(约3×106V/cm)与SiC 材料接近,但受半导体工艺、材料晶格失配等因素影响,GaN 器件的电压耐受能力通常在1000V 左右,安全使用电压通常在650V 以下。随着各项技术难点的克服和先进工艺的开发,GaN 必将作为新一代高效电源器件的制备材料。 (一)GaN 材料结构及特性 GaN 是Ⅲ-V 族直接带隙宽禁带半导体,室温下纤锌矿结构的禁带宽度为3.26eV。GaN 有3 种晶体结构形式,分别为纤锌矿结构、闪锌矿结构和岩盐矿(Rocksalt)结构。其中,纤锌矿结构是Ⅲ族氮化物中较稳定的晶体结构,闪锌矿结构以亚稳相形式存在,而岩盐矿结构是在高压条件下产生的。纤锌矿结构的GaN 材料具有其他半导体所不具备的优异物理性能,如耐化学稳定性、**强硬度、**高熔点等,所以,GaN 基半导体器件具有优异的耐压、耐热、耐腐蚀特性。图4 为GaN 的六方纤锌矿结构和GaN 单晶。 图4 GaN的六方纤锌矿结构(a)与GaN单晶(b) (二)GaN 晶体的制备 GaN 的共价键键能较大(E=876.9kJ/mol),在2500℃熔点下,分解压大约为4.5GPa, 当分解压低于4.5GPa 时,GaN 不熔化直接分解。所以一些典型的平衡方法(如提拉法和布里奇曼定向凝固法等),不再适用于GaN 单晶的生长。目前,只能采用一些特殊的方法来制备单晶,主要包括升华法、高温高压法、熔融结晶法和氢化物气相外延法。其中,前3 种方法对设备和工艺都有严格要求,难以实现大规模的单晶生产,不能满足商业化的要求,而氢化物气相外延(Hydride Vapor-phaseEpitaxy,HVPE)方法是目前研究的主流。大多数可以商业化方式提供GaN 的均匀衬底都是通过这种方法生产的。该技术具有设备简单、成本低、发展速度快等优点。利用金属**化合物化学气相沉淀(Metal-organic Chemical Vapor Deposition,MOCVD)技术可以生长出均匀、大尺寸的厚膜作为衬底。目前,该技术已经成为制备外延厚膜较有效的方法,并且生长的厚膜可以通过抛光或激光剥离衬底,作为同质外延生长器件结构的衬底。 氢化物气相外延层的位错密度随外延层厚度的增加而减小,因此,只要外延层的厚度达到一定值,就可以提高晶体质量。通过HVPE 和空隙辅助分离法(Void-assisted Separation,VAS)可以制备具有高晶体质量和良好再现性的大直径独立GaN 晶片,如图5所示。采用表面覆盖氮化钛(TiN )纳米网的多孔GaN 模板,通过HVPE 生长了厚GaN 层,在 HVPE 生长过程中,这种生长技术在 GaN层和模板之间产生了许多小空隙,当GaN层在生长以后*与模板分开,并且获得独立的GaN 晶片,这些晶片直径较大,表面呈镜面状,无裂缝,位错密度低。 图5 HVPE+VAS法制备具有高晶体质量和大直径独立的GaN 晶片 此外,可以采用MOCVD-GaN / 蓝宝石衬底预处理工艺来制备GaN 厚膜。主要过程为采用等离子体化学气相沉积法在MOCVD-GaN/ 蓝宝石衬底上沉积一层厚度约500nm 的SiO2,然后用电子蒸气机在衬底上蒸镀和锻造一层厚度约20nm 的Ti。退火后在SiO2 表面形成自组装的Ni 纳米团簇,作为光刻掩模。光刻后,将基体置于热HNO3 和氧化腐蚀剂中。去除Ti 和SiO2 后,通过反应离子刻蚀技术沉积一层SiO2,去除表面的SiO2,形成一层SiO2 包裹在边缘的GaN 纳米柱。最后用HVPE 法在表面生长GaN,在冷却过程中,GaN 发生自剥离。图6 为HVPE 和纳米簇自剥离技术制备GaN 单晶的过程示意图。 图6 HVPE+纳米簇自剥离技术制备GaN单晶 上述方法不仅可以实现衬底的自剥离,而且可以形成一种特殊的结构,可以缓冲晶体的生长速度,从而提高晶体的质量,减少内部缺陷。但这些预处理方法相对复杂,会浪费大量时间,并且增加GaN 单晶的成本。 (三)GaN 异质衬底外延技术 由于GaN 在高温生长时N 的离解压很高,很难得到大尺寸的GaN 单晶材料,因此,制备异质衬底上的外延GaN 膜已成为研究GaN 材料和器件的主要手段。目前,GaN的外延生长方法有:HVPE、分子束外延(MBE)、原子束外延(ALE)和MOCVD。其中,MOCVD 是较广泛使用的方法之一。 当前,大多数商业器件是基于异质外延的,主要衬底是蓝宝石、AlN、SiC 和Si。但是,这些基板和材料之间的晶格失配和热失配非常大。因此,外延材料中存在较大的应力和较高的位错密度,不利于器件性能的提高。图7 为衬底材料的晶格失配和热失配关系示意图。 图7 衬底材料的晶格失配和热失配关系 1. SiC 衬底上GaN 基异质结构的外延生长 由于SiC 的热导率远远**GaN、Si和蓝宝石,所以SiC 与GaN 的晶格失配很小。SiC 衬底可以改善器件的散热特性,降低器件的结温。但GaN 和SiC 的润湿性较差,在SiC 衬底上直接生长GaN 很难获得光滑的膜。AlN 在SiC 基体上的迁移活性小,与SiC 基体的润湿性好。因此,通常在SiC 基板上用AlN 作为GaN 外延薄膜的成核层,如图8 所示。许多研究表明,通过优化AlN 成核层的生长条件可以改善CaN 薄膜的晶体质量。但生长在GaN 成核层上的GaN 薄膜仍然存在较大的位错密度和残余应力。AlN的热膨胀系数远大于GaN,在AlN 上生长的GaN 薄膜在冷却过程中存在较大的残余拉应力。拉伸应力会在一定程度上积累,并以裂纹的形式释放应力。另外,AlN 的迁移活性较低,难以形成连续的膜,导致在AlN 上生长的GaN 薄膜位错密度较大。GaN 薄膜中的裂纹和位错会导致器件性能下降甚至失效。由于晶格失配较小,一旦润湿层和裂纹问题得到解决,SiC 衬底上的GaN 晶体质量要优于Si 和蓝宝石衬底上的GaN晶体,因此,SiC 衬底上的GaN 异质结构2DEG 的输运性能更好。 图8 AlN作为过渡层的微观形貌 2. Si 衬底上GaN 基异质结构的外延生长 目前,GaN 基电力电子器件的成本与Si 器件相比仍然非常昂贵。解决成本问题的一途径是利用Si 衬底外延制备GaN 基异质结构,然后利用互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)技术制备GaN 基器件,使器件的性价比**过Si 器件。但与SiC 和蓝宝石衬底相比,Si 衬底外延GaN 要难得多。GaN(0001)与Si(111)的晶格失配率高达16.9%,热膨胀系数失配(热失配)高达56%。因此,Si 衬底上GaN 的外延生长及其异质结构在应力控制和缺陷控制方面面临着严峻的挑战。 外延层材料的晶格常数差异,会导致Si 和GaN 外延层界面处的高密度位错缺陷。在外延生长过程中,大多数位错会穿透外延层,严重影响着外延层的晶体质量。但由于两层热膨胀系数不一致,高温生长后冷却过程中整个外延层的内应力积累很大,发生翘曲并导致外延层开裂。随着衬底尺寸的增大,这种翘曲和开裂现象会越来越明显。 目前,插入层和缓冲层被广泛应用于解决Si 衬底上GaN 异质外延的应力问题,目前主流的3 种应力调节方案如图9 所示。 图9 目前主流的3种应力调节方案(a)低温AlN插入层结构;(b)GaN/AlN**晶格结构;(c)AlGaN缓冲层结构 插入层技术是引入一个或多个薄层插入层来调节外延层的内应力状态,平衡在冷却过程中由热失配和晶格失配引起的外延层的拉应力,目前采用低温AlN 作为插入层来调节应力状态,如图9(a)所示。 缓冲层技术提供了压缩应力来调整外延膜中的应力平衡,目前常用的是AlGaN 梯度缓冲和AlN/(Al)GaN **晶格缓冲,如图9(b)、(c) 所示。上述方法都能提供压应力来平衡Si 基GaN 的拉应力,使整个系统趋于应力平衡。当然,这些方法不能完全解决应力问题。缓冲层的应力调节机制尚不明确,有待于进一步探索和优化。 另外,还有报道采用表面活化键合(SAB)的低温键合工艺将GaN 层转移到SiC 和Si 衬底上,在室温下直接键合制备GaN-on-Si 结构和GaN-on-SiC 结构, 通过氩(Ar)离子束源对晶圆表面进行活化。在表面活化后,两片晶圆将被结合在一起。与Al2O3(蓝宝石)和SiC 衬底上生长的异质外延层的质量相比,Si 衬底上GaN 基异质结构的质量和电性能仍有很大差异。特别是Si 衬底上GaN 外延层存在残余应力和局域陷阱态。这些应力和缺陷控制问题没有从根本上得到解决,导致材料和器件的可靠性问题尤为**。因此,如何在高质量的Si 衬底上制备GaN 基异质结构仍是该领域的核心问题之一。 结束语 高频、大功率、抗辐射、高密度集成宽禁带半导体电子器件的研制,需要优良的材料作基础支撑。高品质的SiC和GaN 器件需要利用外延材料制备有源区,因此,低缺陷衬底和高质量外延层对器件性能起着至关重要的作用。近年来,SiC 和GaN功率器件的制造要求和耐压等级不断提高,对衬底和异质结构(GaN-on-SiC、GaN-on-Si)的缺陷密度及外延薄膜内部的应力平衡状态都提出了更高的要求,目前通过利用AlN 作为过渡层、**晶格缓冲层等提供压应力,进而调节外延层的内部应力以平衡状态,未来对应力调控尚有大量的工作需要进行探索和优化。

仪准科技(北京)有限公司专注于手动探针台,probe,station等

词条

词条说明

白话芯片漏电定位方法科普 原创 仪准科技 王福成 转载请写明出处 芯片漏电是失效分析案例中较常见的,找到漏电位置是查明失效原因的前提,液晶漏电定位、EMMI(CCD\InGaAs)、激光诱导等手段是工程人员经常采用的手段。多年来,在中国半导体产业有个误区,认为激光诱导手段就是OBIRCH。今日小编为大家科普一下激光诱导(laser scan Microscope). 目前激光诱导功能在业内普遍被采

[封装失效分析系列一] IC封装失效分析实验室 近年来,随着半导体技术的不断发展,继续减小线宽的投入与其回报相比变得越来越不划算。业界大佬Intel的10nm工艺预计将在2017年Q3亮相,这个时间点明显已经偏离摩尔定律。高度集成化的芯片,如SoC(systemon chip)的设计与流片成本过高,使得近些年SiP(System in Package)逐渐受到热捧。通过不同种类芯片及封装颗粒之间的

无损检测分析 工程检查/无损检测无损检测是在不损坏工件或原材料工作状态的前提下,对被检验部件的表面和内部质量进行检查的一种测试手段。 无损检测方法 常用的无损检测方法有:X光射线探伤、超声波探伤、磁粉探伤、渗透探伤、涡流探伤、γ射线探伤、萤光探伤、着色探伤等方法。 无损检测目地 通过对产品内部缺陷进行检测对产品从以下方面进行改进。 1、改进制造工艺; 2、降低制造成本; 3、提高产品的可靠性; 4

原来示波器内部如此精巧!深扒示波器原理和结构 示波器是一种使用非常广泛,且使用相对复杂的仪器。本章从使用的角度介绍一下示波器的原理和使用方法。 01示波器工作原理 示波器是利用电子示波管的特性,将人眼无法直接观测的交变电信号转换成图像,显示在荧光屏上以便测量的电子测量仪器。它是观察数字电路实验现象、分析实验中的问题、测量实验结果必不可少的重要仪器。示波器由示波管和电源系统、同步系统、X轴偏转系统、

联系方式 联系我时,请告知来自八方资源网!

公司名: 仪准科技(北京)有限公司

联系人: 赵

电 话: 01082825511-869

手 机: 13488683602

微 信: 13488683602

地 址: 北京海淀中关村东升科技园

邮 编:

相关推荐

相关阅读

1、本信息由八方资源网用户发布,八方资源网不介入任何交易过程,请自行甄别其真实性及合法性;

2、跟进信息之前,请仔细核验对方资质,所有预付定金或付款至个人账户的行为,均存在诈骗风险,请提高警惕!

- 联系方式

- 相关企业

- 青岛福润德微电子设备有限公司

- 泓浒(苏州)半导体科技有限公司

- 光启智能科技(苏州)有限公司

- 键德测试测量系统(东莞)有限公司

- 武汉光旗电子科技有限公司

- 四川九天中创自动化设备有限公司

- 奇河控制技术(苏州)有限公司

- 博捷芯(深圳)半导体有限公司

- 广东瑞乐半导体科技有限公司

- 深圳市聚星州科技有限公司

- 商家产品系列

- 产品推荐

- 资讯推荐