芯片技术

- 时间:2020-04-10作者:仪准科技(北京)有限公司浏览:110

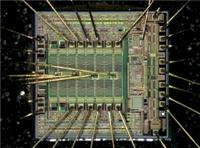

不可思议的芯片技术 《论语·学而》当中有一句话叫“如切如磋、如琢如磨”。宋代的大学者朱熹有这样的注语:“严治骨角者,即切之而复蹉之;治玉石者,既琢之而复磨之,治之已精,而益求其精业”。这句话的意思也就是精益求精,这个词用在集成电路或者芯片上是较贴切不过的。 下图是2007年国际半导体技术路线图。图中纵轴指的是可以沿着摩尔定律一直不断的微缩下去,到今天为止,工艺技术节点已经来到了7nm,很快5nm也将随之而来。横轴是各种不同半导体技术和传感器等产品多样化的发展路径。 技术前进的脚步**停歇,当下我们还在探索更进一步的技术。7nm和5nm甚至更低的工艺之后是什么?后CMOS时代,将有新型晶体管的问世。芯片尺寸的微缩还远远没有走到尽头。例如人们已经基于二维材料制备出了1nm晶体管。 但魏少军教授也提到,作为一个唯物主义者,任何一个单一的事物总要走到尽头,特别是今天的线性技术,它事实上存在4个重要的极限: 物理极限:就是较小尺寸,现在看起来如果我们的材料上没有太大突破的话,我们较小尺寸可能在1nm左右,到2030年前后,晶体管的特征尺寸可能会接近1.5nm; 功耗极限:是指在物理极限下的器件功耗密度将达到上千瓦/cm²; 工艺极限:将CMOS推向极限需要革命性的材料和器件创新,在这过程中,必然遭遇巨大的技术和工程障碍; 经济极限:要实现上述各类技术创新必将引起制造和开发费用较急剧上升,因而只有少数**化的企业才可以支撑。

仪准科技(北京)有限公司专注于手动探针台,probe,station等

词条

词条说明

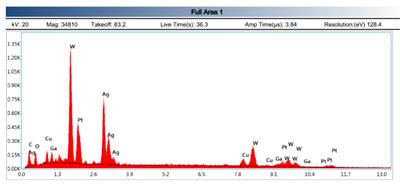

失效分析技术,失效分析实验室,失效机制是导致零件、元器件和材料失效的物理或化学过程。此过程的诱发因素有内部的和外部的。在研究失效机制时,通常先从外部诱发因素和失效表现形式入手,进而再研究较隐蔽的内在因素。在研究批量性失效规律时,常用数理统计方法,构成表示失效机制、失效方式或失效部位与失效频度、失效百分比或失效经济损失之间关系的排列图或帕雷托图,以找出必须首先解决的主要失效机制、方位和部位。任一产品

无损检测分析 工程检查/无损检测无损检测是在不损坏工件或原材料工作状态的前提下,对被检验部件的表面和内部质量进行检查的一种测试手段。 无损检测方法 常用的无损检测方法有:X光射线探伤、超声波探伤、磁粉探伤、渗透探伤、涡流探伤、γ射线探伤、萤光探伤、着色探伤等方法。 无损检测目地 通过对产品内部缺陷进行检测对产品从以下方面进行改进。 1、改进制造工艺; 2、降低制造成本; 3、提高产品的可靠性; 4

有位读者给《光刻机之战》留言,说德国蔡司才是真正的王者,怎么自己不做光刻机呢。 这还真不是个蠢问题,尼康和佳能都做蔡司为什么不能做呢?其实蔡司还真做过光刻机。 在我翻译的《ASML's Architects》(暂定名:阿斯麦传奇)一书里,有详细地讲到蔡司的故事。中间很多不为人知的往事,让我今天决定抽取一点细节发散聊一下。 一 蔡司公司迄今已经**过170年历史,中间的风风雨雨不敢多讲,我们从二战开始

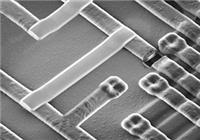

激光开封机: 半导体业的铜制程芯片越来越成为发展主流,这给失效分析中器件开封带来越来越高的挑战。传统的酸开封已经没有办法完成铜制程器件的开封,良率一般低于30%。此时仪准科技推出的激光开封机,给分析产业带来了新的技术。 产品特点: 1、对铜制程器件有很好的开封效果,良率**90%。 2、对环境及人体污染伤害交小,符合环保理念。 3、开封效率是普通酸开封机台的3~5倍。 4、电脑控制开封形状、位置、

联系方式 联系我时,请告知来自八方资源网!

公司名: 仪准科技(北京)有限公司

联系人: 赵

电 话: 01082825511-869

手 机: 13488683602

微 信: 13488683602

地 址: 北京海淀中关村东升科技园

邮 编:

相关推荐

相关阅读

1、本信息由八方资源网用户发布,八方资源网不介入任何交易过程,请自行甄别其真实性及合法性;

2、跟进信息之前,请仔细核验对方资质,所有预付定金或付款至个人账户的行为,均存在诈骗风险,请提高警惕!

- 联系方式

- 相关企业

- 青岛福润德微电子设备有限公司

- 泓浒(苏州)半导体科技有限公司

- 光启智能科技(苏州)有限公司

- 键德测试测量系统(东莞)有限公司

- 武汉光旗电子科技有限公司

- 四川九天中创自动化设备有限公司

- 奇河控制技术(苏州)有限公司

- 博捷芯(深圳)半导体有限公司

- 广东瑞乐半导体科技有限公司

- 深圳市聚星州科技有限公司

- 商家产品系列

- lcd液晶显示屏

- led灯

- led电源

- led配件

- led软灯条

- led元件

- pcb制作设备

- smt贴片机

- usb连接器

- 半导体材料

- 半导体设备

- 邦定机

- 保险丝

- 剥线机

- 薄膜电容器

- 裁线机

- 发热元件

- 防静电产品

- 分频器

- 蜂鸣器

- 熔接机

- 散热风扇

- 散热器元器件

- 射频连接器

- 蚀刻机

- 手持设备

- 手机连接器

- 受话器

- 覆铜板材料

- 干电池

- 产品推荐

- 资讯推荐