IC封装失效分析实验室

- 时间:2020-04-13作者:仪准科技(北京)有限公司浏览:111

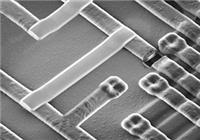

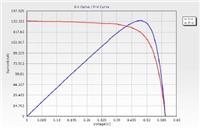

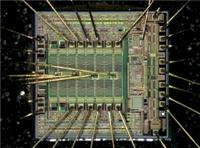

[封装失效分析系列一] IC封装失效分析实验室 近年来,随着半导体技术的不断发展,继续减小线宽的投入与其回报相比变得越来越不划算。业界大佬Intel的10nm工艺预计将在2017年Q3亮相,这个时间点明显已经偏离摩尔定律。高度集成化的芯片,如SoC(systemon chip)的设计与流片成本过高,使得近些年SiP(System in Package)逐渐受到热捧。通过不同种类芯片及封装颗粒之间的组合封装,可以针对不同客户的需求,用相对较低的成本实现高度集成化的目标,封测产业的春天已然到来。日趋复杂的封装形式,如WireBond+Flip-chip,Interposer+TSV,PoP,甚至WLP等,相应的新失效模式也层出不穷,因此封装级别的失效分析显得日趋重要。 封测大厂一般都拥有自己的失效分析实验室,而有些中小工厂则在搭建中或没有自己的实验室,只能依靠第三方实验室。这里简单比较一下第三方实验室与工厂自有实验室的差别。 先来聊聊第三方实验室,首先是设备种类多,各种高大上的设备一应俱全,而且几乎每台设备都会配一个经验丰富的工程师,保证了分析结果的专业性。同时,大多数第三方实验室已经营多年,获得了国内或者国外的各种认证,这些认证对于OEM或军方客户非常重要,因为他们往往比较认可第三方实验室的分析结果。但对于一个工艺相对稳定且产量很高的封测厂来说,较看重的却是分析的效率。因为对于量产的工厂来说,其追求的目标就是用较低的成本生产出较多的合格品。因此对于收率异常的物料,必须马上找到失效的原因,并反馈到设备工程师来进行改善。只有形成 生产→REJ分析→找到失效原因→反馈生产→工艺改善→生产 的良性循环,生产工艺才会越来越稳定,成本才会越来越低。可以看到,在这个循环里失效分析是关键,而在这方面,自有实验室相比第三方实验室来说就有着得天*厚的优势。因为自有实验室的分析人员对自家的产品十分了解,失效信息的全面性直接保证了分析的效率与结果的准确性。诚然,一般自有实验室在设备种类,人员素质等方面与第三方实验室还有不小的差距,但够用才是硬道理。根据以往经验,一个较完善的自有实验室完全可以解决掉大约95%的案子。 那么什么样的失效分析实验室才是合格的呢?光有好设备是不够的,还要有像样的技术和配套的管理,也就是失效分析实验室的三要素。 对于失效分析来说,设备是**位的,所谓巧妇难为无米之炊,没有称手的设备再好的技术也发挥不出来。而某些设备,比如Thermal,EMMI/InGaAs/OBIRCH,3D X-ray,FIB等则直接决定了一个失效分析实验室水准的高低。*二位的是技术,包括磨样(平磨,侧磨,断面,去层),观察,缺陷或失效定位。对于封测领域,Die Level的不良或缺陷虽然只占总体不良或缺陷的10%左右,但能否进行Die Level的分析却是一个封装级别失效分析实验室在技术领域的分水岭。 最后再说一说失效分析实验室的日常管理,通常包括以下几个内容:分析任务分配,设备日常保养,标准作业流程,分析人员培训,分析耗材采购等。个人认为,一个好的失效分析实验室体系中人员和流程同样重要。标准的分析流程可以解决掉大部分的案子,而一个完善的失效分析实验室也不会因为某个牛人的离开而垮掉。一个公司对于失效分析的重视程度决定了其失效分析实验室的规模,而失效分析技术也非一日所成,需要不断的磨练与改良,同时辅以较正规的管理,三要素之间形成良性循环,失效分析会越做越好,才能更好的为公司服务。失效分析团队是失效分析实验室的灵魂,可以这样说,是否拥有一个合格的失效分析团队是一个封测厂能否快速处理工程异常,保证产品可靠性,处理客户投诉,增加单位产出,并进一步提高良率的关键。 下图给出了一个标准的封装级别失效分析实验室应该具有的分析设备以及分析人员的比例。 作为半导体产业的中下游,封测厂的技术层次相对较低。很多封测厂无论是工程能力还是良品率还只是将将及格的水平,而失效分析就是那个能帮助封测厂从及格做到优秀的一法宝。 (本文旨在提出如何建立一个标准的封装级别的失效分析实验室,仅供参考。失效分析的核心技术是失效定位,封装失效分析也不例外,下一篇就跟大家分享一下对于封装级别分析较重要的——热定位设备的相关技术与经验) 芯片开封实验室介绍,能够依据国际、国内和行业标准实施检测工作,开展从底层芯片到实际产品,从物理到逻辑全面的检测工作,提供芯片预处理、侧信道攻击、光攻击、侵入式攻击、环境、电压毛刺攻击、电磁注入、放射线注入、物理安全、逻辑安全、功能、兼容性和多点激光注入等安全检测服务,同时可开展模拟重现智能产品失效的现象,找出失效原因的失效分析检测服务,主要包括点针工作站(Probe Station)、反应离子刻蚀(RIE)、微漏电侦测系统(EMMI)、X-Ray检测,缺陷切割观察系统(FIB系统)等检测试验。实现对智能产品质量的评估及分析,为智能装备产品的芯片、嵌入式软件以及应用提供质量保证。

仪准科技(北京)有限公司专注于手动探针台,probe,station等

词条

词条说明

失效分析是一门发展中的新兴学科,近年开始从**向普通企业普及。它一般根据失效模式和现象,通过分析和验证,模拟重现失效的现象,找出失效的原因,挖掘出失效的机理的活动。在提高产品质量,技术开发、改进,产品修复及仲裁失效事故等方面具有很强的实际意义。其方法分为有损分析,无损分析,物理分析,化学分析等。 原理 失效机制是导致零件、元器件和材料失效的物理或化学过程。此过程的诱发因素有内部的和外部的。在研究失

透视半导体测试设备:芯片良率的扞卫者 从两起并购说起 2018年3月,美国半导体设备制造商KLA-Tencor花34亿美元现金加股票鲸吞了以色列半导体设备制造商奥宝科技。 无*有偶,两个月后,先前向美国外国投资**(CFIUS)打小报告的美国半导体企业科休(Cohu)宣布将以7.96亿美元现金加股票收购Xcerra。 这两起并购都发生在半导体测试设备领域,引起了各方的高度关注。本次就让我们窥探半

湖北省集成电路产业 在国家大力推动下,国内集成电路产业逐渐形成了以北京为核心的京津翼地区、以上海为核心的长三角地区、以深圳为核心的珠三角地区、以四川、重庆、湖北、湖南、安徽等为核心的中西部地区四大产业聚集区。 随着新一轮集成电路发展热潮涌现,除京沪等地继续**外,中西部地区省市虽为*二梯队,却也因西安、成都、重庆、武汉、长沙、合肥等集成电路重点城市,成为产业发展较活跃的产业聚集区,其中湖北凭借着国

失效分析技术,失效分析实验室,失效机制是导致零件、元器件和材料失效的物理或化学过程。此过程的诱发因素有内部的和外部的。在研究失效机制时,通常先从外部诱发因素和失效表现形式入手,进而再研究较隐蔽的内在因素。在研究批量性失效规律时,常用数理统计方法,构成表示失效机制、失效方式或失效部位与失效频度、失效百分比或失效经济损失之间关系的排列图或帕雷托图,以找出必须首先解决的主要失效机制、方位和部位。任一产品

联系方式 联系我时,请告知来自八方资源网!

公司名: 仪准科技(北京)有限公司

联系人: 赵

电 话: 01082825511-869

手 机: 13488683602

微 信: 13488683602

地 址: 北京海淀中关村东升科技园

邮 编:

相关推荐

相关阅读

1、本信息由八方资源网用户发布,八方资源网不介入任何交易过程,请自行甄别其真实性及合法性;

2、跟进信息之前,请仔细核验对方资质,所有预付定金或付款至个人账户的行为,均存在诈骗风险,请提高警惕!

- 联系方式

- 相关企业

- 青岛福润德微电子设备有限公司

- 泓浒(苏州)半导体科技有限公司

- 光启智能科技(苏州)有限公司

- 键德测试测量系统(东莞)有限公司

- 武汉光旗电子科技有限公司

- 四川九天中创自动化设备有限公司

- 奇河控制技术(苏州)有限公司

- 博捷芯(深圳)半导体有限公司

- 广东瑞乐半导体科技有限公司

- 深圳市聚星州科技有限公司

- 商家产品系列

- 产品推荐

- 资讯推荐